Samsung Foundry is set to information its 2nd generation 3 nm-class fabrication innovation along with its performance-enhanced 4 nm-class production procedure at the upcoming upcoming 2023 Seminar on VLSI Innovation and Circuits in Kyoto, Japan. Both innovations are necessary for the agreement maker of chips as SF3 (3GAP) assures to provide concrete enhancements for mobile and SoCs, whereas SF4X (N4HPC) is developed particularly for the most requiring high-performance computing (HPC) applications.

2 nd Generation 3 nm Node with GAA Transistors

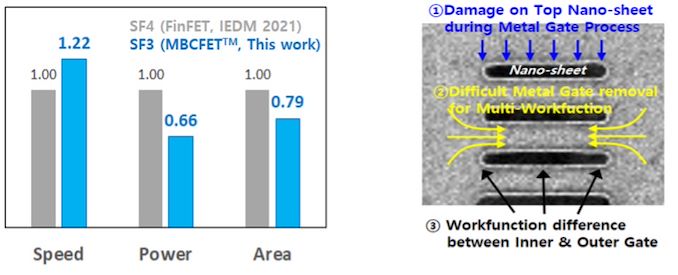

Samsung’s upcoming SF3 (3GAP) procedure innovation is an improved variation of the business’s SF3E (3GAE) fabrication procedure, and depends on its second-generation gate-all-around transistors– which the business calls Multi-Bridge-Channel field-effect transistors (MBCFETs). The node assures extra procedure optimizations, though the foundry chooses not to compare SF3 with SF3E. Compared to its direct predecessor, SF4 (4LPP, 4nm-class, low power plus), SF3 declares a 22% efficiency increase at the exact same power and intricacy or a 34% power decrease at the exact same clocks and transistor count, along with a 21% reasoning location decrease. Though it is uncertain whether the business has actually attained any scaling for SRAM and analogue circuits.

In addition, Samsung declares that SF3 will supply extra style versatility helped with by differing nanosheet (NS) channel widths of the MBCFET gadget within the exact same cell type. Oddly, variable channel width is a function of GAA transistors that has actually been gone over for many years, so the method Samsung is phrasing it in context of SF3 may indicate that SF3E does not support it.

So far neither Samsung LSI, the corporation’s chip advancement arm, nor other consumers of Samsung Foundry have actually officially presented a single highly-complex processor standardized on SF3E/3GAE procedure innovation. In truth, it appears like the only publicly-acknowledged application that utilizes the market’s very first 3 nm-class fabrication procedure is a cryptocurrency mining chip, according to TrendForce This is not especially unexpected as use of Samsung’s ‘early’ nodes is usually rather restricted.

By contrast, Samsung’s ‘plus’ innovations are usually utilized by a wide variety of consumers, so the business’s SF3 (3GAP) procedure is most likely to see much greater volumes when it appears at some point in 2024.

SF4X for Ultra-High-Performance Applications

In addition to SF3, which is developed for a range of possible usage cases, Samsung Foundry is prepping its SF4X (4HPC, 4 nm-class high-performance computing) developed for performance-demanding applications like datacenter-oriented CPUs and GPUs.

To deal with such chips, Samsung’s SF4X uses a efficiency increase of 10% combined with a 23% power decrease. Samsung does not clearly define what procedure node that contrast is being made versus, however most likely, this protests their default SF4 (4LPP) fabrication innovation. To attain this, Samsung revamped transistors’ source and drain after reassessing their tensions (most likely under high loads), carried out even more transistor-level design-technology co-optimization (T-DTCO), and presented a brand-new middle-of-line (MOL) plan.

The brand-new MOL allowed SF4X to provide a silicon-proven CPU minimum voltage (Vmin) of 60mV, a 10% reduction in the variation of off-state present (IDDQ), ensured high voltage (Vdd) operation at over 1V without efficiency destruction, and an enhanced SRAM procedure margin.

Samsung’s SF4X will be a competitor for TSMC’s N4P and N4X nodes, which are due in 2024 and 2025 respectively. Based upon claim specificaitons alone, it is tough to inform which innovation will provide the very best mix of efficiency, power, transistor density, effectiveness, and expense. That stated, SF4X will be Samsung’s very first node in the current years that was particularly architected with HPC in mind, which suggests that Samsung has (or is anticipating) enough client need to make it worth their time.